This article is intended to introduce how the convergence to affect the result of HFSS.

本文以兩個相同疊構的microstrip傳輸線為例(一個的reference plane是用perfect_E boundary,一個的reference plane是用有實際厚度的pec),說明在HFSS內的設定如果不洽當,後者會得到不準確的結果。主要原因是:使用HFSS這類純3D FEM模擬軟體時,必須注意所切的網格數目是否足夠,即adaptive mesh是否收斂以得到夠精確的結果。這是在HFSS上一個非常重要且基礎的觀念,但很多資深使用者還是常疏忽的地方。

HFSS using Perfect_E Boundary as Reference Plane

HFSS using Real Conductor Thickness as Reference Plane (not accurate enough)

HFSS using Real Conductor Thickness as Reference Plane (more accurate)

問題與討論

4.1 本文的例子,為何HFSS內的solution frequency取到20GHz這麼高?

4.2 如何讓step1.3與step3的結果更接近?

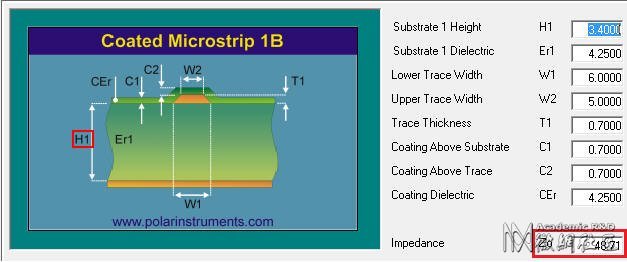

1.1 四層板很容易可以做到特性阻抗45~50歐姆。

1.2 在HFSS建一個疊構同上圖的100mils microstrip line,特性阻抗模擬結果如下

1.3 如果把reference plane改成[Finite Conductor] boundary, and set material [copper] with 0.7mils thickness,特性阻抗模擬結果如下

承上,reference plane改成有實際厚度的pec,並且這厚度從0.5mils sweep to 3mils,特性阻抗模擬結果如下

特性阻抗變化差異頗大,而且沒有隨厚度變化的趨勢,這並不合理,所以這結果是有問題的

Change [Max. Delta S] from 0.02 to 0.001, and [Min. Number of Passes] from 1 to 2

特性阻抗變並沒有隨reference plane厚度變化而有太大的改變,這比較合理

4.1 本文的例子,為何HFSS內的solution frequency取到20GHz這麼高?

Ans:因為要看Tr=20ps的TDR,所以extract model的頻寬要夠

4.2 如何讓step1.3與step3的結果更接近?

Ans:Change [Max. Delta S] from 0.02 to 0.001, and [Min. Number of Passes] from 1 to 2

這結果與本文step1.1用Polar試算的幾乎一模一樣

an008_convergence_affect.zip (89.55 KB)

an008_convergence_affect.zip (89.55 KB)