doherty功放的仿真问题: 本帖最后由 xy-nwpu 于 2010-3-26 15:52 编辑

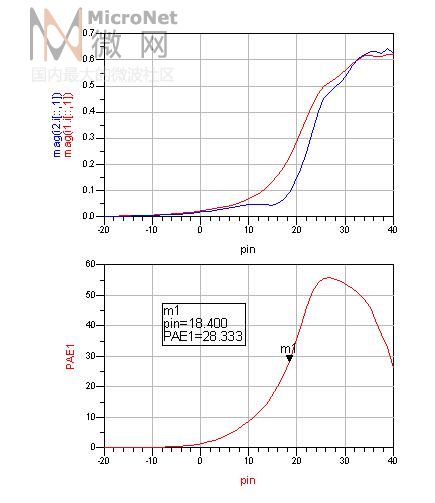

用飞思卡尔的MW6S004N做doherty功放,但是仿真了很多次都没有得到如下图有两个波峰的效率曲线(如图)

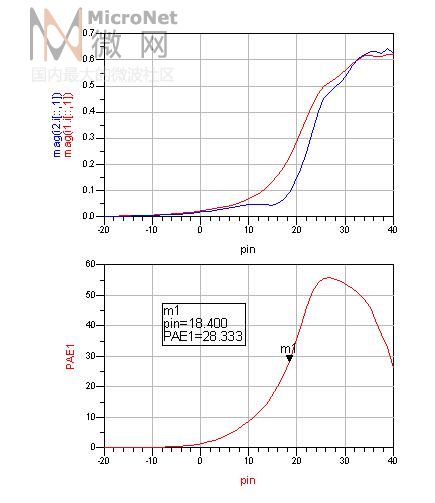

而我仿真出来的效率图为(上面的一个为载波和峰值功放的电流曲线):

也就是说功率回退没有起到作用,请问各位遇到过类似问题吗?我仿真了很多种情况,一种是

载波功放和峰值功放的输入输出匹配都一样,另一种情况是载波匹配到高效率,峰值功放则匹配到高增益,

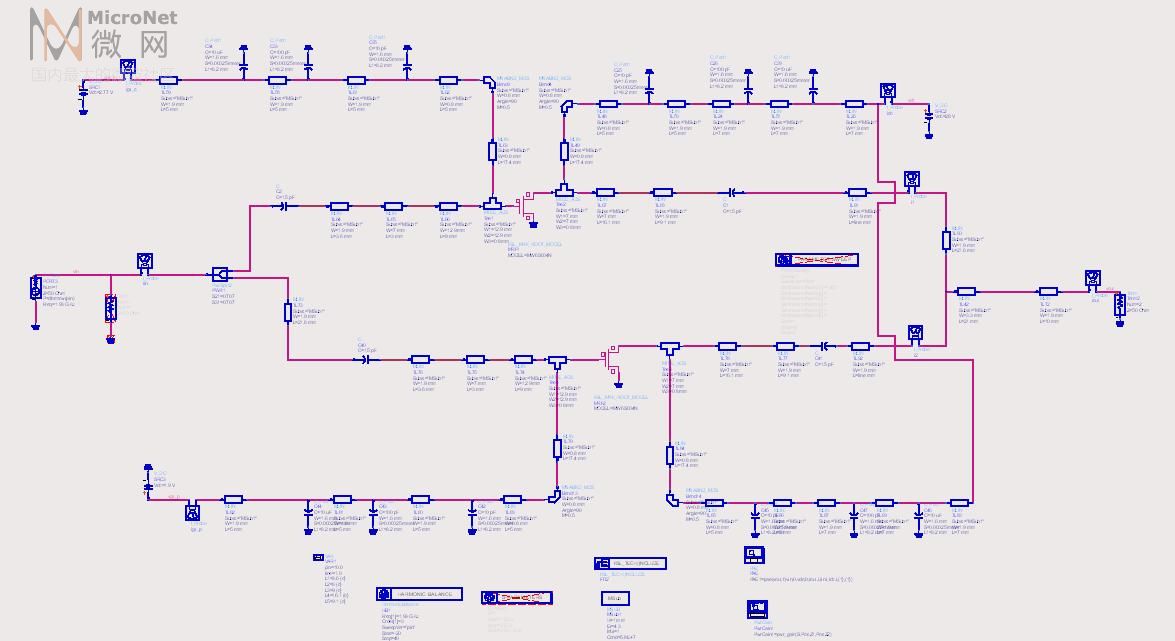

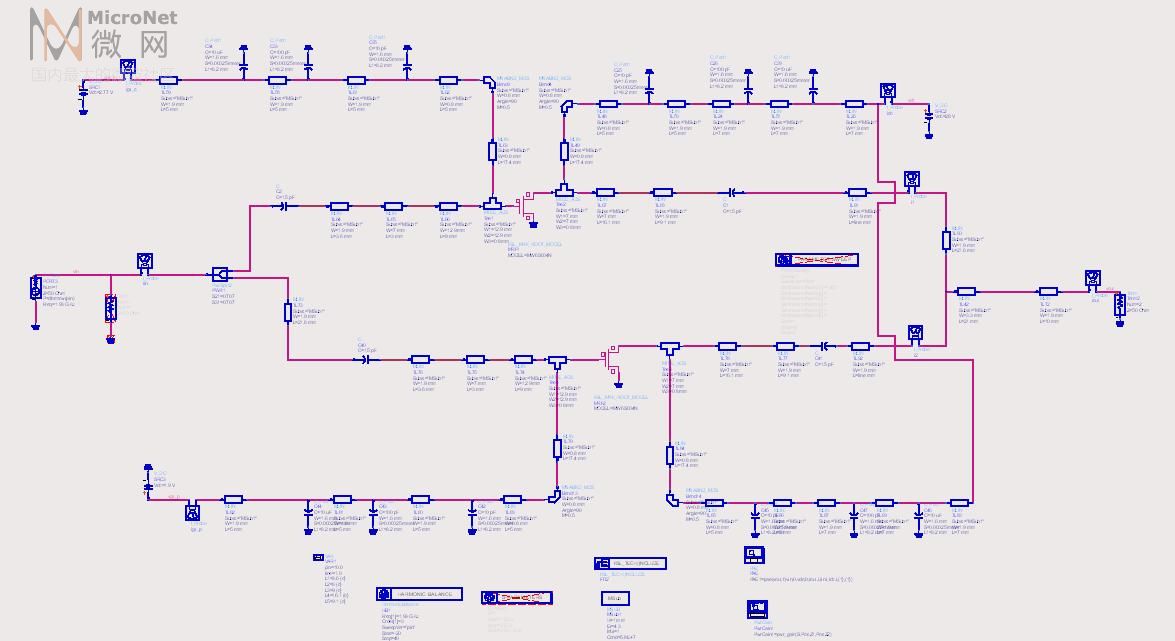

然而两种情况仿真出来的效率都如此,我的仿真工程文件图和工程文件如下:

请各位指教!

怎么没人回答呢,自己先顶一个

幫你推一下!!順便學習~~

求高人指点指点,不甚感激!

顶一个!!!!!!!!!!

请教各位前辈了,在线等!!!!!

顺便学习一下

增加四分之一波长线的特征阻抗。或者降低一点PPA的偏置。

貌似楼主用的是相同的管子和even walkinson搭的doherty,为什么要这样做呢?

我再看看,稍后回答你。

增加四分之一波长线的特征阻抗。或者降低一点PPA的偏置。

貌似楼主用的是相同的管子和even walkinson搭的 ...

jetfighter 发表于 2010-3-30 17:43

我扫描了一下PPA的偏置,但是没有实际效果。我用相同的管子也是从实际情况考虑,因为管子很难搞到,何况用不同的管子了。

增加特征阻抗似乎关系不大,我打听了一下,一个成电的仁兄说freescale管子在实际建模的时候就是基于AB类或者A类的,在C类偏置

的时候就相当不准了,所以当PPA偏置在C类的时候效率很难上的去。有没有仁兄用freescale的管子仿真过呢,是否遇到相同问题?

我前面说的结论是从理论(理想模型中)得到的,可能同时调整两个因素才会有效果。

摩托罗拉的管子,尤其是LDMOS,特性曲线有很强的二阶效应,补偿了AB类功放的非线性,所以搭出来的AB类功放的增益是平坦的。但如果偏置在B类状态,未必能够获得平坦增益,也许适当提高工作点效果会好一点。只是个人猜测,我下载的摩托罗拉的designkit中没有楼主的管子,没办法仿真。

另外,RF功放这块理论和实际脱节比较大,呵呵。

我也用楼主提供的哪个原理图给仿真了以下,发现将PK功放的栅压写为0,就可以得到上面的哪个波形,但是效率好象只有53左右,而上图的是63作用,所以我怀疑是PK管的栅压肯能写的不对,不知道对不对?

我也用楼主提供的哪个原理图给仿真了以下,发现将PK功放的栅压写为0,就可以得到上面的哪个波形,但是效率好 ...

dqw1002 发表于 2010-3-31 22:03

我也是一下,看看栅压为0时,能不能得到那个曲线。

结果怎么样,顺便问一下,你的那个SMT_Pad的那个控件是在那个库里面找的?

突然发现一个很严重的问题,PK功放好像有点自激,我把main功放的栅压写为0,只让PK功放工作,发现pk功放在低功率是有一个尖峰,很可能是自激了,你在确认一下。我把偏置供电线的微带线的长度改了一下,但是那个信号还是没消失,理论上的偏置供电线的长度应该是1/4波长线,但是我发现你的偏置供电线,大于了1/4波长。

突然发现一个很严重的问题,PK功放好像有点自激,我把main功放的栅压写为0,只让PK功放工作,发现pk功放在低 ...

dqw1002 发表于 2010-4-1 23:33

那个控件就是在artwork里面有的啊。我的偏置线可能是长了一点点吧,但是这个不会影响出现两个波峰的的吧 唉 真郁闷 到现在还是没有办法解决两个波峰效率曲线的问题。

呵呵,我这几天也在学习这块的知识,既然你确定电路没问题,那你在看看你效率的计算公式,你的ids_c在pk功放和main功放的合路上,所以算效率的时候我认为只算ids_c就行了,就不需要在单独算ids_p。

还有就是,你算效率的计算方式和我看的参考书上的效率计算方式不大一样,参考书上它算Pdc时它是用 Is_h=real(ID.i[0]) Is_l=real(IG.i[0]) Vs_l=real(VG[0]) Vs_h=real(VD[0])Pdc=Is_h*Vs_h+Is_l*Vs_l+1e-20 的函数代替算得,好像只算了实部,而你那样直接算的话可能把虚部也包括进去了,我是这样理解的不知道对不对,你在想一下。我也用上面的方式试了一下,Vs_l和Vs_h可以替代成功,就是Is_l和Is_h,无法识别,郁闷啊!

问题可能有以下几点

1. 首先要看你用的管子适合不适合做DOHERTY结构,也就是说你可以先设计一个CLASS B匹配到50欧姆,然后把50欧姆用90度IMPENDANCE INVERTER换成100欧姆,然后看相应的电流,效率。

2. 你的PPA在back-off POWER LEVEL上的输出阻抗有没有达到无穷,否则会有LEACKAGE CURRENT效应。

3. 你用的相同的晶体管,也就是说,在最大输入能量的时候,PPA不能提供相同的电流,所以也没办法完成TWO PEAK EFFICIENCY.

bil0901@hotmail.com

有问题的话可以联系我

还没看你的工程文件的。。因为自己的电脑在跑ACLR。。恩。。

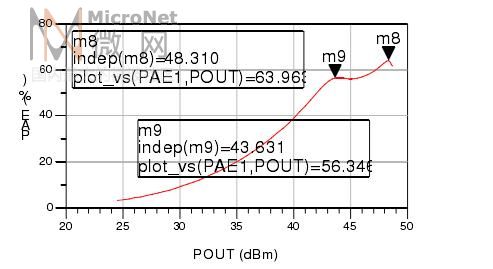

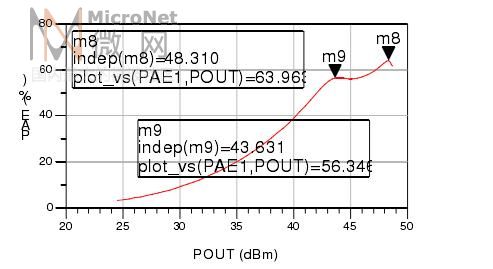

从PAE曲线来看确实有很多问题。。对于传统的Doherty结构来说。第一个效率峰值应该出现在单管功率峰值的回退3dB的功率点,MW6S004N管的PEP在4W,那么理论上应该在2W的时候出现第一个效率峰值点,即在32dBm。而你的曲线图在26dBm就出现第一个效率峰值。。。造成这种结果的原因有很多。等下细看一下你的工程文件吧

还有。。从电流曲线图来看,传统的Doherty一般情况是载波放大器偏置在AB类,峰值放大器偏置在C类,我不知道你的峰值放大器偏置在B类还是C类,但是从电流曲线图来看峰值放大器提前工作了。。。

因为从理论上说要出现PAE双峰的曲线的话,在小功率输入信号时,载波放大器工作,峰值放大器由于偏置点低,不工作。随着功率的增加,载波放大器饱和,此时载波放大器的输出阻抗端是匹配到2R点,使用高的负载阻抗来达到效率的提前饱和。。。然后峰值放大器才开始工作。。当然,这是理论上的。。但是你的电流曲线图看的话峰值放大器在载波放大器开始工作一会也开始工作了。。。即载波放大器还没有饱和工作过峰值放大器就工作了,因此从这个角度分析不可能出现双峰PAE曲线了

楼上的,认识一下吧?

呵呵,你仿真结果图也太差了吧,没具体看你的电路,给不出具体的解决方法

顺便附图给你,看看对你有没什么帮助,

在顺便问下,你这个是应用在什么系统?是不是Active Antena?

楼上说的有道理,顶一下

刚看了你的项目文件,感觉上你的电路偏置不太对;

你试下把VGS_M改为3.01,而VGS_P改为0.8,应该有改善很多。

(个人观点):你上面给的那个结果图是不可能达到的,除非你换管子。

新手过来学习

谢谢各位,给了我很多启发。我也问过一位电子科大的同学,他的意思是我用的飞思卡尔管子在建模的时候就是基于A或者AB类的,如果偏置在C类的话就很不准了。意思是偏置在C类的话效率不会很明显上升,这样就影响了峰值功放的效率,所以整体效率也是一个问题。还有我觉得峰值功放提前工作的问题也是他们在建模的时候基于AB或A类的了。如果哪位用过飞思卡尔管子成功做出了两个峰值效率功放曲线的图,请点一下,谢谢了QQ:1076972830

飞思卡尔的管子做出两个峰值效率的功放曲线图么。。。有几个管事可以的。。恩。。。。比如我现在正在用的MRF6S21140H的管就可以,不过老实说匹配不好做,因为它的输出阻抗有点太小了。。呵呵。。还有飞思卡尔推荐的专门用于Doherty结构的几个管也可以,,我还试过其他的管,,倒是蛮多出不来双峰的就是了。。。。

想传个PAE的双峰曲线图。。。咋弄?一定要弄成JPG格式么?QQ截图的好像不行。。呵呵

学习一下{:7_1234:}

reverse_prj.rar (2.94 MB)

reverse_prj.rar (2.94 MB)